Design of Register using Verilog

This page provides an overview of Verilog, its significance, and practical examples of digital design using Verilog. We will explore three fundamental designs in this experiment:

- T-Flip Flop

- Counter

- T-Flip Flop Using D-Flip Flop

Verilog is a hardware description language (HDL) developed to model electronic systems. It enables designers to describe the structure and behavior of digital circuits, facilitating simulation, synthesis, and verification. The modular nature of Verilog allows for efficient design, testing, and reuse of code.

1. T-Flip Flop

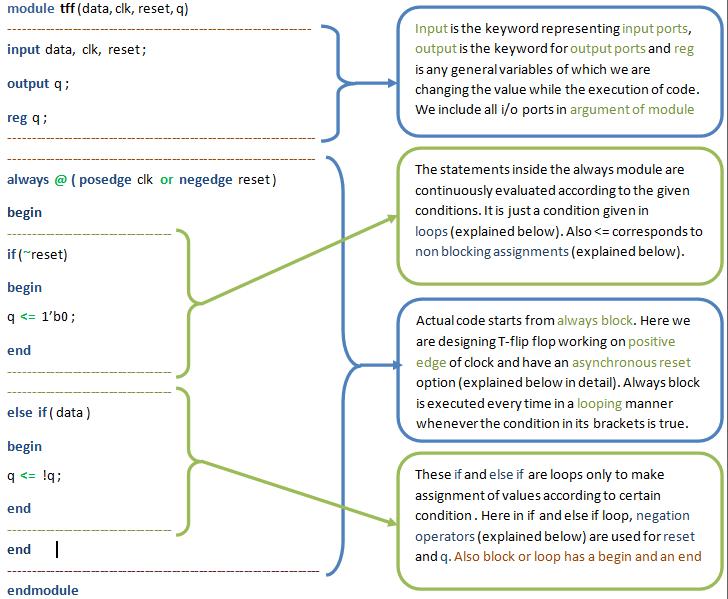

The Verilog code for a T-Flip Flop is shown below, accompanied by an explanation of its components:

Key Concepts

Module:

A module is the fundamental building block in Verilog. It can represent a single element or a collection of lower-level design blocks. Modules encapsulate functionality and expose interfaces through input and output ports, allowing for abstraction and reuse.Module Name:

The module name is user-defined and is used to instantiate the module elsewhere in the design. Instantiation is demonstrated in the third example.Module Arguments:

Similar to function arguments in C, module arguments specify the input and output ports used for communication with other modules or the external environment.Input/Output Ports:

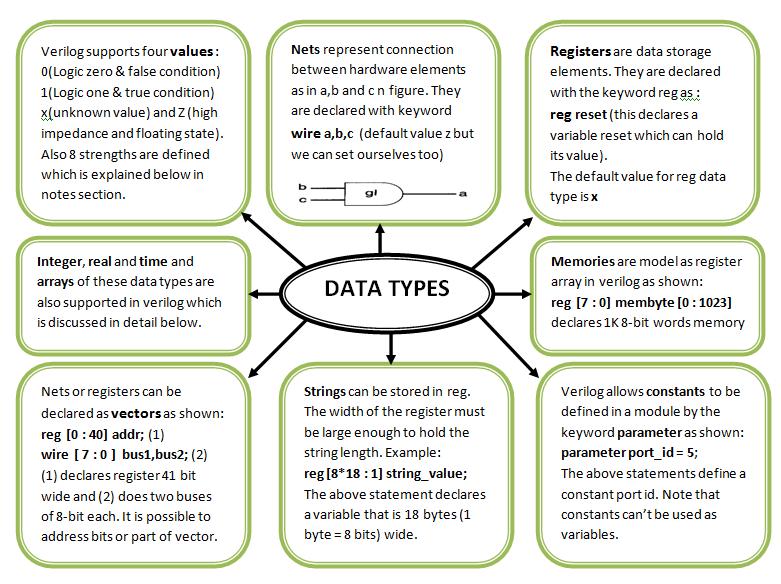

These ports facilitate data transfer into and out of the module. All arguments listed in the module declaration must be defined as either input or output within the module.Data Types:

In this example, theregdata type is used. Other data types, such aswire, will be introduced in subsequent examples. Refer to the chart below for an overview of Verilog data types:

Always Block:

Thealwaysblock contains statements that execute repeatedly, triggered by changes in specified signals (e.g., clock or reset).Posedge Clock:

Theposedge(positive edge) of the clock triggers the execution of statements within thealwaysblock, corresponding to a transition from low to high voltage.Negedge Reset:

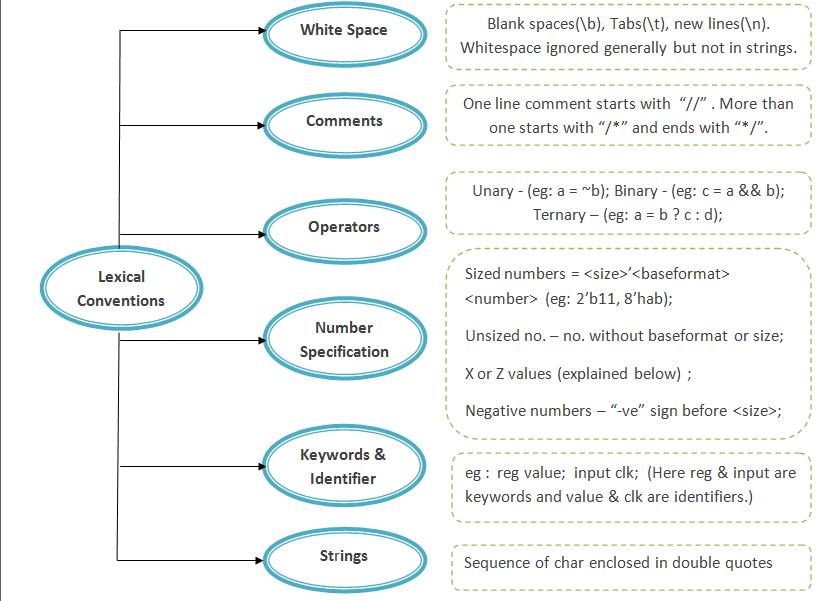

Thenegedge(negative edge) of the reset signal asynchronously sets the output to zero, regardless of the clock.Operators and Lexical Conventions:

Operators such as~(bitwise NOT) and!(logical NOT) are used in Verilog. The chart below summarizes various operators and conventions:

Loops:

Verilog supports control structures such asfor,if-else, andwhile, similar to C. These structures usebeginandendto define statement blocks.Blocking and Non-Blocking Assignments:

- Blocking (

=): Statements execute sequentially. - Non-Blocking (

<=): Statements execute concurrently.

For example:

Botha = b; b = a;aandbwill have the value ofb.

Using non-blocking assignment:

The values are swapped simultaneously.a <= b; b <= a;

- Blocking (

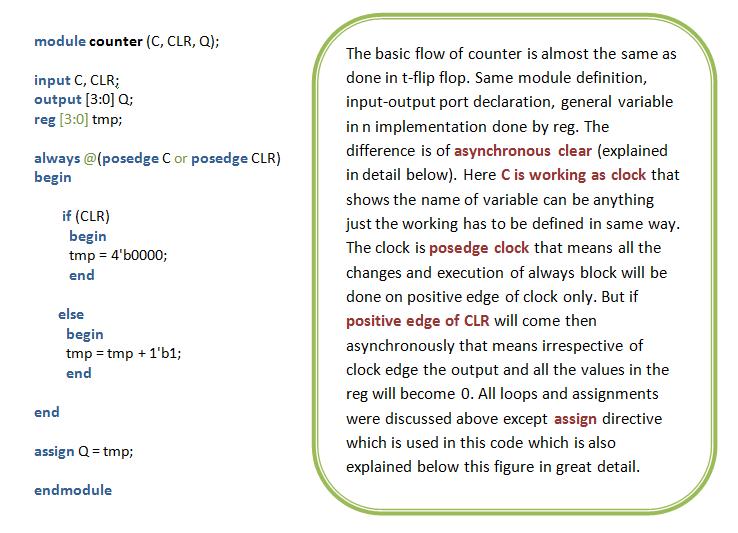

2. Counter

The Verilog code for a counter is provided below, with explanations for each part:

Additional Notes

- Assign Statement:

Theassignkeyword is used for continuous assignment. For example,assign Q = tmp;ensures thatQis updated immediately whenevertmpchanges, regardless of execution sequence.

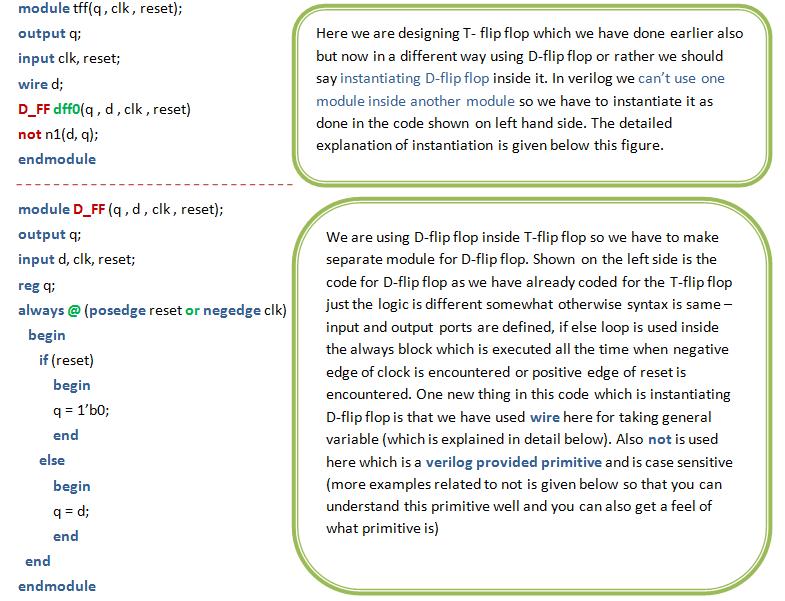

3. T-Flip Flop Using D-Flip Flop

The Verilog code for implementing a T-Flip Flop using a D-Flip Flop is shown below:

Key Concepts

Module Instantiation:

Modules are not defined within other modules; instead, they are instantiated (called) as needed. The module is referenced by its original name, but each instance must have a unique identifier. For example, the moduleD_FFis instantiated asdff0.Verilog Primitives:

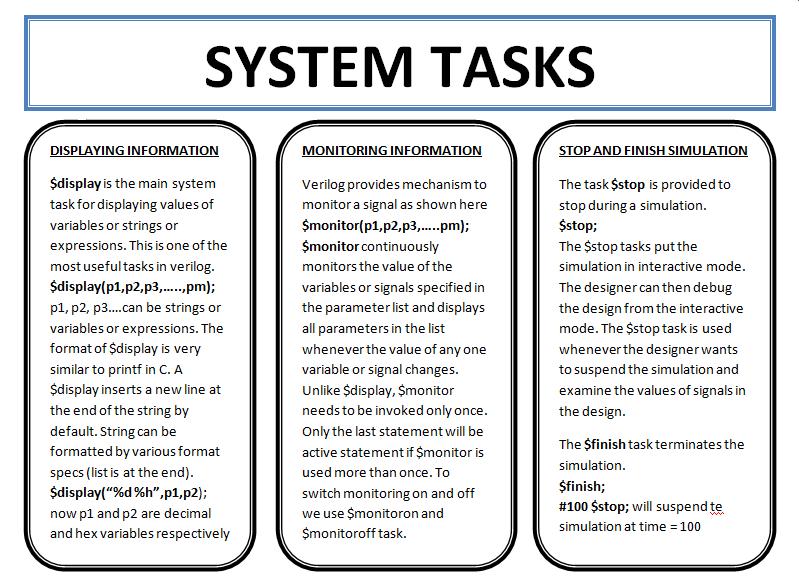

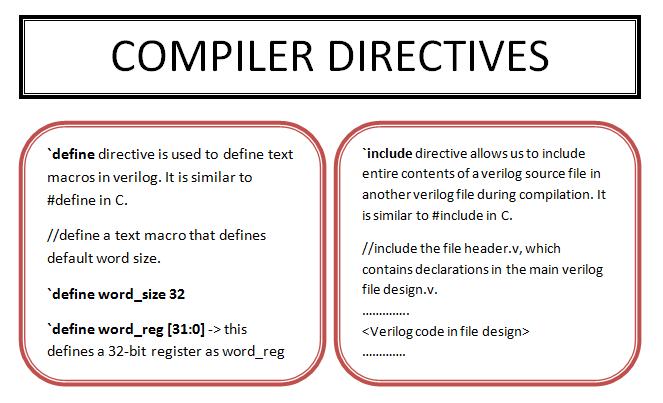

Verilog provides built-in primitives such asnot. Innot (d, q);,dis the output andqis the input.Compiler Directives and System Tasks:

While not used in the above examples, Verilog supports compiler directives and system tasks for advanced functionality. Refer to the flowcharts below for more information:

Introduction to Registers

Registers are fundamental building blocks in digital systems that store binary data. They are essentially a collection of flip-flops that can store multiple bits of information. In this experiment, we focus on a specific type of register called the Serial In Serial Out (SISO) register.

SISO Register

A SISO register is a type of shift register where:

- Data enters the register one bit at a time (serial input)

- Data exits the register one bit at a time (serial output)

- Data moves through the register one position at each clock cycle

Working Principle

- The register consists of a chain of D flip-flops

- Each flip-flop's output is connected to the input of the next flip-flop

- The first flip-flop receives the serial input

- The last flip-flop provides the serial output

- On each positive clock edge, data shifts one position to the right

Verilog Implementation

The SISO register is implemented using:

- A 4-bit register to store the data

- An always block triggered by the positive edge of the clock

- Non-blocking assignments for sequential logic

- A reset signal to initialize the register

Timing Characteristics

- Setup Time: The time before the clock edge when input data must be stable

- Hold Time: The time after the clock edge when input data must remain stable

- Clock-to-Q Delay: The time taken for the output to change after the clock edge

Applications

SISO registers are used in:

- Serial data transmission

- Data buffering

- Time delay circuits

- Pattern recognition

- Serial-to-parallel conversion

Verilog Concepts Used

Sequential Logic

- always @(posedge clk) blocks

- Non-blocking assignments (<=)

- Reset signals

Data Types

- reg for sequential elements

- wire for combinational connections

Vector Operations

- Bit concatenation

- Bit slicing

Testbench Design

- Clock generation

- Reset sequence

- Input stimulus