Full Subtractor using 4:1 MUX.

Introduction

Full Subtractor

Different variants of an adder and a subtractor form an integral part of modern ICs and are found in Arithmetic Logic Units (ALUs) and the digital Signal Processing (DSP) units. A half subtractor is a combinational circuit that performs subtraction of two binary bits. It has two inputs (minuend and subtrahend) and two outputs Difference (D) and Borrow (Bout). Half-subtractor is used to subtract the LSB of the subtrahend to the LSB of the minuend when one binary number is subtracted from another. Subtraction is done according to the rules of binary subtraction. A disadvantage of the Half Subtractor circuit is that there is no provision for a ‘Borrow-in’ from the previous circuit when subtracting multiple data bits from each other. A full subtractor circuit takes into account this borrow-in input from the previous circuit. In Full Subtractor circuit there are three inputs, A which is Minuend, B which is Subtrahend and Borrow in (Bin) of the previous stage and two outputs Difference (D) and Borrow out (Bout). The Boolean expressions for Difference and Borrow are

Difference = A⊕B⊕Bin

Borrow = A'.Bin + B.Bin + B.A'

The operations can be summarized in a truth table as,

Table-1: Truth table of full subtractor

| S. No. | Input | Output | |||

|---|---|---|---|---|---|

| A | B | Bin | Difference D | Borrow Bout | |

| 1 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 | 1 |

| 3 | 0 | 1 | 0 | 1 | 1 |

| 4 | 0 | 1 | 1 | 0 | 1 |

| 5 | 1 | 0 | 0 | 1 | 0 |

| 6 | 1 | 0 | 1 | 0 | 0 |

| 7 | 1 | 1 | 0 | 0 | 0 |

| 8 | 1 | 1 | 1 | 1 | 1 |

Full subtractor can be implemented using a 4:1multiplexer.

Multiplexer

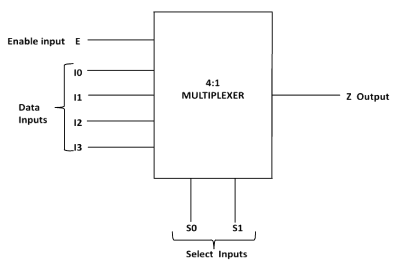

A multiplexer is a combinational circuit which selects binary information present on any one of the input lines, depending upon the logic status of the selection inputs, and routes it to the output line. If there are m selection lines, then the number n of maximum possible input lines is 2m and the multiplexer is referred to as a n-to-1 multiplexer. A 4:1 multiplexer (Fig. 1) has 4 input lines and 2 selection lines. Table 2 shows the output of a 4:1 multiplexer.

Fig-1: A 4:1 Multiplexer

Table-2: Truth table of 4:1 Multiplexer

| Select Lines | Output | |

|---|---|---|

| S0 | S1 | Z |

| 0 | 0 | I0 |

| 0 | 1 | I1 |

| 1 | 0 | I2 |

| 1 | 1 | I3 |

Implementation of a Full Subtractor using 4:1Multiplexer

In a full subtractor there are three inputs and A, B and Bin and two outputs D and Bout. The Booleanfunctions for Difference and Borrow in SOP form are as follows:

Bout(A,B,Bin)= Σ(1,2,3,7)

In view of these the output table of full subtractor can be rewritten as

Table-3: Output of full subtractor in terms of input

| S. No. | Input | Output in terms of Bin | |||

|---|---|---|---|---|---|

| A | B | Bin | Difference D | Borrow Bout | |

| 1 | 0 | 0 | 0 | Bin | Bin |

| 2 | 1 | ||||

| 3 | 0 | 1 | 0 | Bin' | 1 |

| 4 | 1 | ||||

| 5 | 1 | 0 | 0 | Bin' | 0 |

| 6 | 1 | ||||

| 7 | 1 | 1 | 0 | Bin | Bin |

| 8 | 1 | ||||

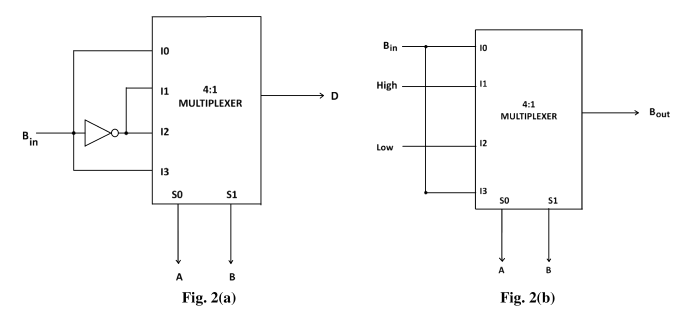

On comparing tables 2 and 3 we find that the difference and borrow bits of full subtractor can be implemented using 4:1 multiplexer as follows:

The selection lines of the multiplexer be given values as per the two inputs A and B of the full subtractor.

For Difference Output

Two input lines of the multiplexer be given values corresponding to third input Bin of the subtractor and other two lines be given its complemented values Bin'.

For Borrow Output

Two input lines be given input values corresponding to third input Bin of the subtractor and out of rest two one is always high and the other is always low.

The diagrammatic representation is given in Figures 2(a) and 2(b):

Fig.-2: Implementation of (a) Difference and (b) Borrow outputs of a full subtractor with a 4:1 multiplexer

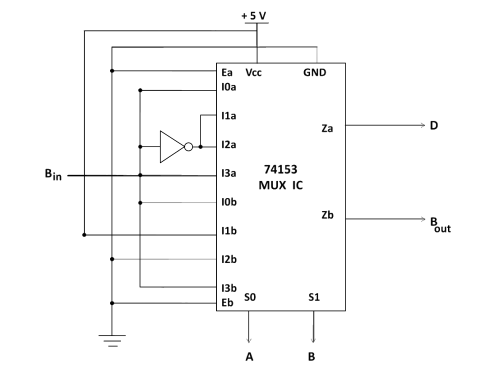

In the experiment the Full subtractor circuit is designed using a dual multiplexer IC 74153 and a NOT gate IC7404.

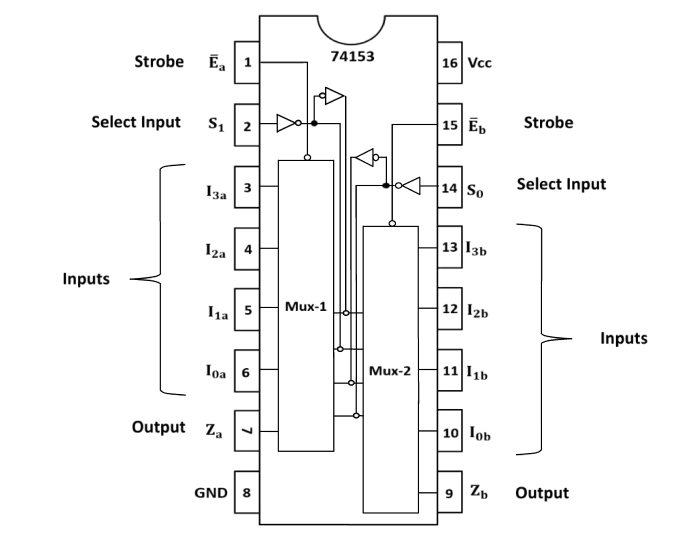

74153 Multiplexer IC

The 74153 IC is a dual 4 input multiplexer with common selection lines S0 and S1 and individual active LOW enable inputs Ea and Eb for each section.It can select two bits of data Ia and Ib from up to four sources.The selection lines control the particular input to be multiplexed and sent to the output Zi (i = a, b). The two buffered outputs present data in the true (non-inverted) form. When the Enables (Ea, Eb) are HIGH, the corresponding outputs (Za, Zb) are forced LOW. The pin diagram is shown in fig 3. More details can be found on Datasheet.

Pin Name

S0,S1 - Common Select Input

E - Enable (Active LOW) Input

I0, I1, I2, I3 - Multiplexer Inputs

Z- Multiplexer Output

Fig.3-Pin diagram of 74153 MUX IC

Fig.-4: Circuit diagram of full subtractor using 74153 MUX

Table-4: Function table of 74153 MUX IC for full subtractor

| Select inputs | Inputs (a) | Inputs (b) | Output | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S0 | S1 | I0a | I1a | I2a | I3a | I0b | I1b | I2b | I3b | Za | Zb | ||

| A | B | Bin | Bin' | Bin' | Bin | Bin | 1 | 0 | Bin | D | Bout | ||

| 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | I0a | 0 | I0b | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | ||

| 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | I1a | 1 | I1b | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | ||

| 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | I2a | 1 | I2b | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | ||

| 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | I3a | 0 | I3b | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | ||

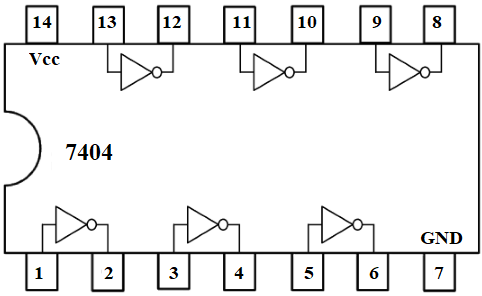

The pin diagram of 7404 NOT gate IC is shown in fig 5.

Fig.-5: Pin diagram of IC 7404

Application Of Full Subtractor

- These are generally employed in ALU (Arithmetic logic unit) in computers to subtract and in CPU and GPU for the applications of graphics to decrease the circuit difficulty.

- Subtractors are mostly used for performing arithmetical functions likesubtraction, in electronic calculators as well as digital devices.

- These are also applicable in different microcontrollers forarithmetic subtraction, timers, and program counter (PC).

- They are also useful for DSP and networking-based systems.