Cyclic codes

The theory associated with Experiment-8 is divided into two parts:

- Basics of cyclic codes

- Shift register based encoder and decoder

1. Basics of cyclic codes

Cyclic codes form an important subclass of linear block codes. In this section, we will introduce definition and basic properties of cyclic codes.

A detailed discussion of the topics covered in these notes can be found in [1, Chapter 5]. In this Experiment, we will focus on binary cyclic codes. In Experiment-7, we had introduced Reed-Solomon codes. Note that Reed-Solomon codes form a class of non-binary cyclic codes.

In Experiment-3, we studied Hamming codes, which are binary cyclic codes.

Let us first define the operation of cyclic shift of a vector. Consider a vector .

Then the vector obtained by shifting cyclically to the right -times is given by

. For a cyclic code, as the name suggests, cyclic shift of any codeword is also a codeword. This property precisely defines a cyclic code.

A linear block code is said to be a cyclic code if every cyclic shift of a codeword is also a codeword in the given code .

Before providing other properties of cyclic codes, let us consider a simple example for a cyclic code. Consider a linear block code of length and dimension

with the set of codewords given by . Observe that any cyclic shift of a codeword is again a valid codeword and hence this linear block code is a cyclic code. Students are encouraged to revisit Experiment-3 and verify that Hamming codes indeed follow this property and are cyclic codes.

For cyclic codes, it is convenient to represent its codewords using polynomials. The polynomial representation of vector , denoted by , is given by

Let denotes the set of polynomials with the coefficients chosen from . Thus the polynomial in .

For the given cyclic code , there exists a polynomial in such that any codeword in can be written as

where is the polynomial corresponding to the message . For multiplying two polynomials in , the individual additions and multiplications of the corresponding coefficients should be performed over (details can be found in the theory of Experiment-1, Part-1). See Eq.(5) discussed below for an illustration of multiplication of two polynomials in . Observe that the maximum degree of a codeword polynomial will be and similarly the maximum degree of a message polynomial can be .

The polynomial defined in Eq.(3) is called as the generating polynomial of the code and the corresponding cyclic code is said to be generated by its generating polynomial . We now summarize some of the properties of the generating polynomial. Details can be found in [1, Section 5.1]. The proofs of these properties are out of scope for our current experiment, however students are encouraged to verify these properties for Examples-1 and 2 given below.

- For the given cyclic code , the generating polynomial is the non-zero codeword of the minimum degree.

- The generating polynomial of a cyclic code is unique.

- Degree of the generating polynomial is equal to .

- Suppose . Then we have .

- A generator matrix of the code can be written directly using its generating polynomial as follows,

- The generating polynomial is a factor of the polynomial .

Let us consider some examples of cyclic codes.

1. Consider the cyclic code of length and dimension with the set of codewords given by . Suppose , , , .

The polynomial representations of these codewords are given below Observe that every codeword is a multiple of the polynomial and hence it is the generating polynomial of the code. Using property-5, can you write down a generating matrix of this code?

2. : Consider a cyclic code of length generated by the generator polynomial . Note that this is Hamming code of length studied in Experiment-3.

A codeword in this code can be obtained by multiplying the message polynomial with the generator polynomial , i.e., . For example, the codeword corresponding to the message polynomial is given by

It can be seen from Eq.(5) that the codeword corresponding to message vector will be .

All possible codewords of this code can be obtained by considering the message polynomials corresponding to all possible vectors in . These are tabulated below. Students are encouraged to verify the calculations towards this by themselves.

2. Shift register based encoder and decoder

For encoding a message using a cyclic code, one can consider a generator matrix of the given code and obtain the corresponding codeword as , since cyclic code is a linear block code. However, cyclic codes have rich algebraic structures and this allows to perform encoding operation much efficiently. Similarly, while one can perform decoding of cyclic codes via standard array and syndrome decoding (see Experiment-4), owing to these structural properties, decoding can be performed efficiently. In this experiment, we shall focus on shift register based encoder and decoder for cyclic codes.

2.1 Shift register based encoder

Let us first study shift register based encoder for a cyclic code of length and the generator polynomial (recall that ). Suppose we wish to encode the message polynomial . Let be the remainder obtained when the polynomial is divided by . Then it can be shown that (for proof refer [1, Section 5.1]) the corresponding codeword will be given by

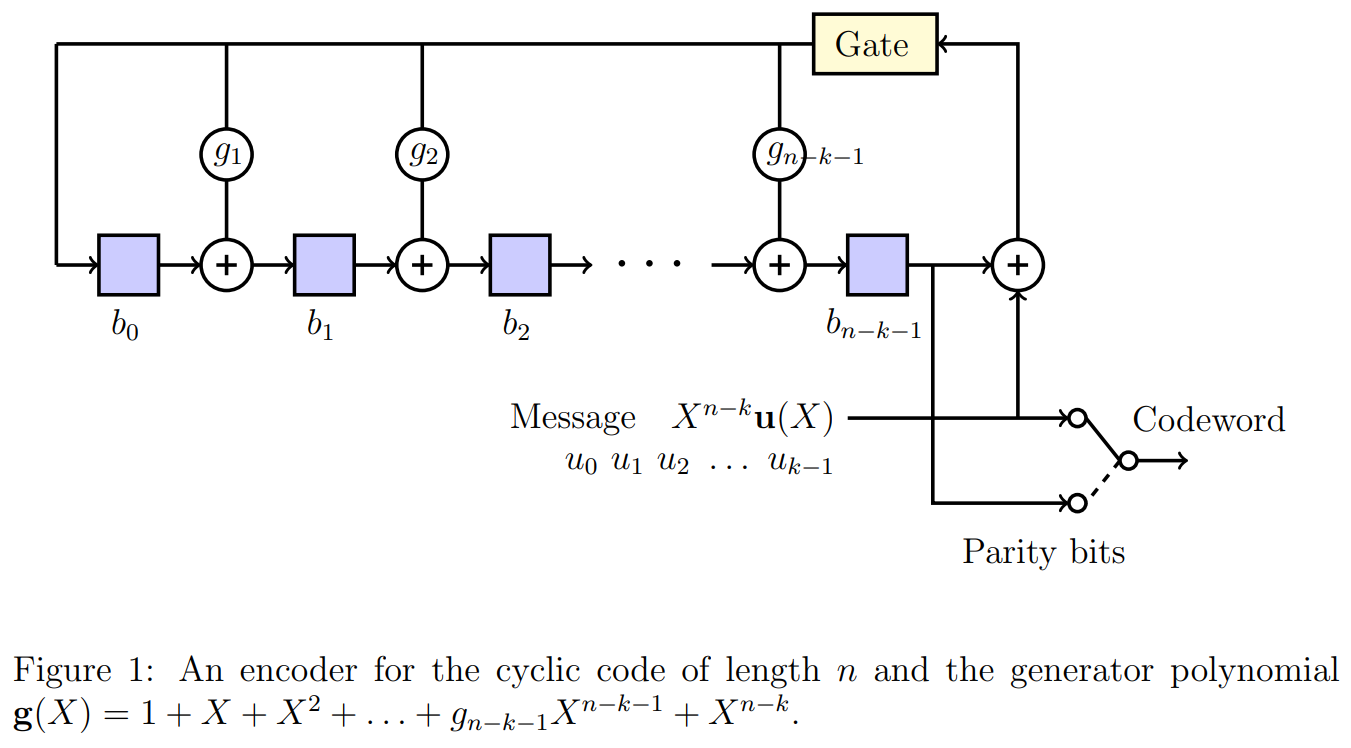

We shall next see how Eq.(6) can be implemented using shift registers. The encoding circuit corresponding to this is shown in Figure 1. When the value of , the corresponding connection will present, for . Similarly when , the corresponding connection will not be there. Observe that there are shift registers. The contents of the shift registers are denoted by . Note that when the operation of the circuit is completed, the values of will provide the coefficients of the required remainder polynomial .

- The contents of all shift registers are initialized to zero.

- Turn on the gate.

- At -th time instant, message bit is available at the input. Note that the message bit enters the system first, followed by , and so on.

- First perform all the computations (at the outputs of all XOR gates) using the present values of the shift registers and the input message bit . This will provide the values of the shift registers for the next time instant.

- Steps 3 and 4 should be performed for time instances.

- Turn off the gate after time instances, i.e., when the computations corresponding to all message bits are completed.

- The contents of the shift registers will now provide the coefficients of the remainder polynomial .

- To obtain the final codeword, the switch is kept at the message bits for the initial time instances and on the parity bits for the remaining time instances. Thus the final codeword is will be

Let us consider Example-2 to illustrate encoding steps. The encoder for Example-2 is shown in Figure 2. Suppose at some time instant, the contents of the shift register are and the input message bit is . Then at the next time instant, contents of the shift registers will be .

2.2 Shift register based decoder

In Experiment-4, we studied syndrome decoding for linear block codes. The key steps in syndrome decoding consist of computing the syndrome of the received vector and associating it with the error pattern, which is then added to obtain the decoded codeword. For cyclic codes, these operations can be performed efficiently using a shift register based decoder, and the cyclic structure allows us to decode a received vector serially, which will be discussed in this section.

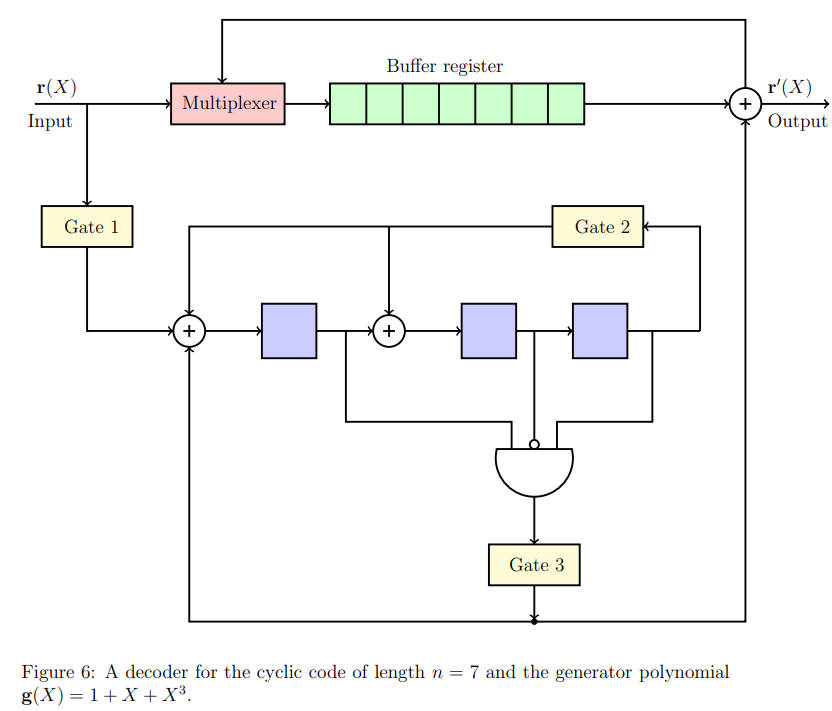

In Section 2.2.1, we discuss syndrome computations in cyclic codes that are useful in decoding. In Section 2.2.2, we briefly explain a general decoder of an cyclic code. A detailed explanation of a specific Meggitt decoder for cyclic code generated by provided in Section 2.2.3. Recall that the encoding of this code is covered in Section 1, Example-2.

2.2.1. Syndrome computations in cyclic code

Let us recall the syndrome decoding method of a linear block code provided in Section-2 of Experiment-4. For the given linear block code with parity check matrix , for any received vector , we find the corresponding syndrome as . However, in cyclic codes, we determine the syndrome of by calculating the syndrome polynomial of the received polynomial . The syndrome of is . Dividing by the generator polynomial , we obtain

The remainder is a polynomial of degree or less, and its corresponding vector representation is the syndrome of . In this division, since the polynomials belong to , the individual additions and multiplications of the corresponding coefficients should be performed in . From Eq. (3), it is clear that the syndrome is identical to zero if and only if the received polynomial is a code polynomial. The calculation of a syndrome is illustrated with the following example.

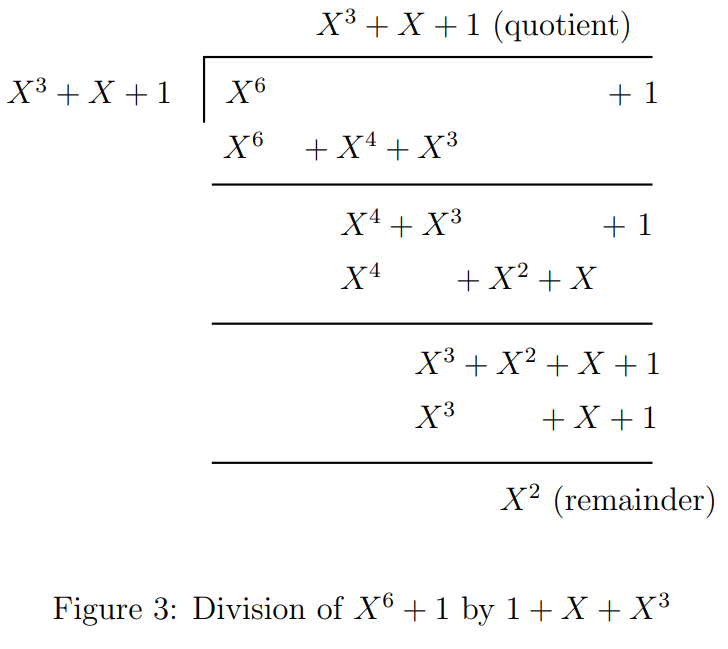

Consider the cyclic code generated by . Suppose the received vector , then its corresponding received polynomial . From Eq. (7), the syndrome is the remainder when divided by . The division operation between and is given in Figure 3. The remainder obtained from this division is . Hence, the syndrome and

Dividing by to obtain the remainder can be accomplished by the division circuit as shown in Figure 4. This circuit is referred as the syndrome circuit, and its shift register is known as the syndrome register. The syndrome circuit is identical to the -stage encoding circuit as shown in Figure 1. But the only difference is that the received polynomial is shifted into the register from the left end instead of the right end.

A few properties of the syndrome that are useful in decoding cyclic codes are listed below without proof.

- The polynomial is a cyclic shift of . The syndrome of is denoted by . The syndrome is the remainder obtained by dividing by the generator polynomial (for proof, refer [1, Section 5.4]). The syndrome for can calculate with the same syndrome circuit as follows.

Use as the initial contents in the syndrome register and disable the input gate. Perform a single shift operation on the syndrome circuit. Then, the resultant values contained in the syndrome register is .

Suppose and is the syndrome of . Let is the cyclic shift of , i.e., . Then the syndrome of

- for is . This syndrome can also be obtained with the same syndrome circuit. Use as the initial contents in the syndrome register and disable the input gate. Add from the left end of the syndrome circuit by shifting the syndrome register once. Then the syndrome will form in the syndrome register (for proof refer [1, Section 5.5]).

- for , . Similarly, by following the above mentioned procedure, we obtain the syndrome . The only difference is to add from the left end of the syndrome circuit instead of .

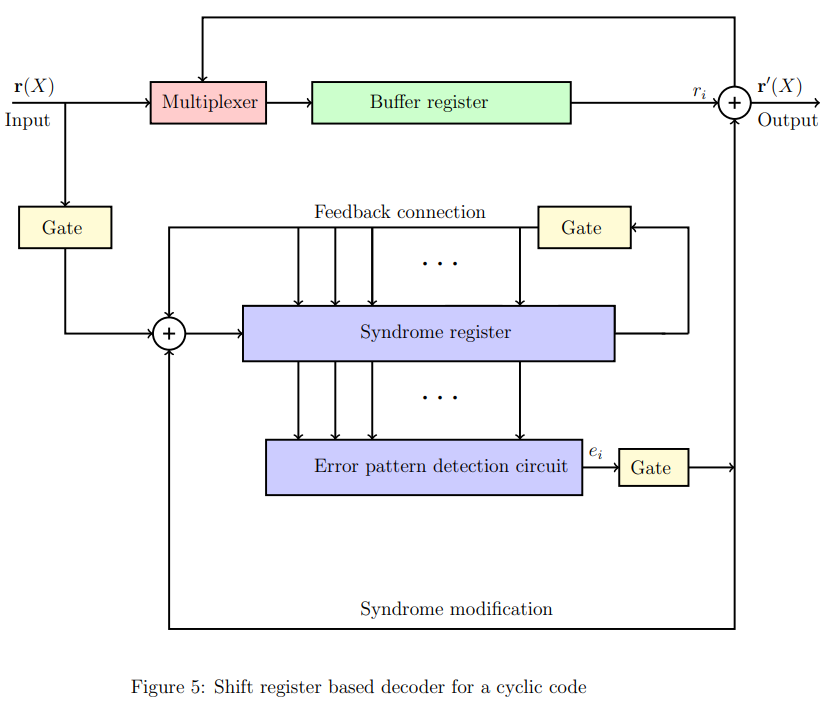

2.2.2. General decoder

A general decoder of a cyclic code (shown in Figure 5), consists of three major parts: (1) a syndrome register, (2) an error-pattern detector, and (3) a buffer register to store the received vector. The received polynomial is shifted into the syndrome register from the left end. The syndrome is formed by shifting the entire received vector into the syndrome register. To compute the syndrome, the syndrome circuit (Figure 4) of the given code is being used. The received vector is simultaneously stored in the buffer register. After time instances, the entire received vector is stored in the buffer register, and the corresponding syndrome will form in the syndrome register.

After forming the syndrome in the syndrome register, the error detection and correction process starts serially from bit to . The contents of the syndrome register are fed to the error-pattern detector, which is a combinational logic circuit. It is designed in such a way that the output of the detector is if there is an error in the rightmost bit of the register, otherwise . To remove the error effect in the syndrome and received vector, the following operation takes place in the decoder at the same time instant: i) the syndrome register and buffer register shifted once, ii) the output of the error-pattern detector is fed into the syndrome register from the left end through an XOR gate and iii) the output is also fed into the buffer register through an XOR gate. The above operation will be done number of time instances to correct all the bits of . Notice that during each shift operation, the vector in the buffer register gets modified, and its corresponding syndrome is formed in the syndrome register. For a more detailed understanding of a general decoder, students can refer to [1, Section 5.5]. Hereafter, we will look into the entire decoding process of a Meggitt decoder.

2.2.3. Meggitt decoder

In syndrome decoding (refer to Experiment-4), we use a syndrome table that consists of syndromes of all correctable erasure patterns. Those syndromes are called error syndromes. The Meggitt decoder in cyclic codes is a method for error correction that efficiently computes error syndromes and corrects errors using a limited number of error syndromes. This approach eliminates the necessity for a syndrome table. In the context of a single-error-correcting code, the Meggitt decoder is simple and appropriate. It can determine all syndromes based on just one error syndrome.

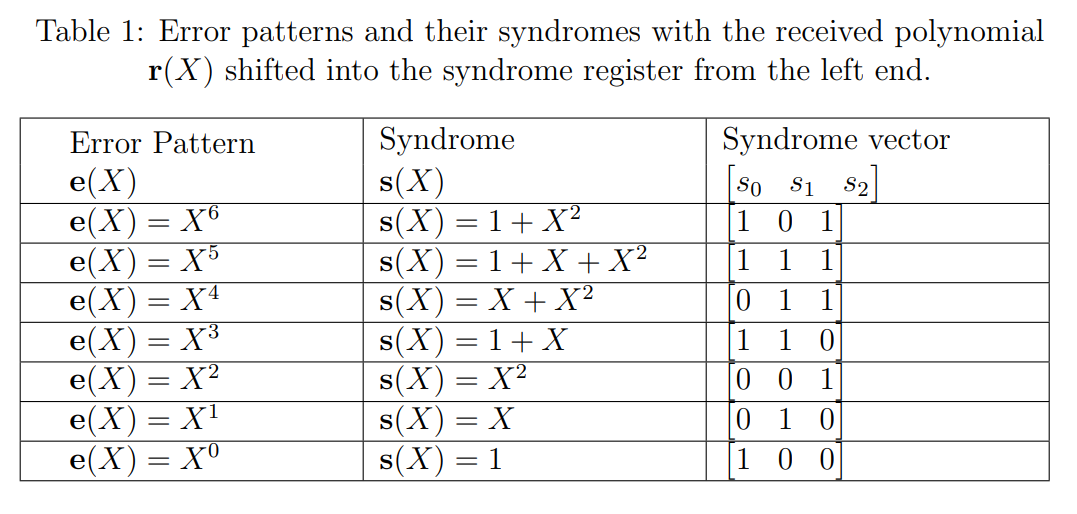

In this experiment to discuss the Meggitt decoder, we consider the decoding of a cyclic code generated by . This code has a minimum distance of 3 and is capable of correcting any single error over a block of seven bits. A single error can occur anywhere in the received vector. Suppose the error occurred in the received vector at th location (), then its error pattern has zeros at all positions except at and its corresponding error polynomial .

The seven single-error patterns and their corresponding syndrome are listed in Table 1. Among all these syndromes, our aim is to find one such error syndrome that determines all error syndromes for this Meggitt decoder. In the Meggitt decoder, the design of the error pattern detection circuit depends upon that particular error syndrome.

Recall the decoding process of a general decoder. The task of the error pattern detection circuit is to determine if the rightmost bit of the vector in the buffer register contains an error. This can be achieved by examining the corresponding syndrome formed in the syndrome register. Typically, finding an error pattern detector is crucial for a decoder. In some cases, error pattern detection circuits are simple. The error pattern detection circuit for cyclic code generated by is discussed below.

- Suppose there is an error in the rightmost bit of the buffer register, then the error pattern polynomial . We see that is the only error pattern with an error at location . When this error pattern occurs, the syndrome in the syndrome register will be after the entire received polynomial has entered the syndrome register. The detection of this syndrome indicates that is an erroneous bit and must be corrected.

- Suppose that a single error occurs at location [i.e., ] for . After the entire received polynomial has been shifted into the syndrome register, the syndrome in the register will not be . However, after another shifts, the contents in the syndrome register will be , and the next received bit to come out of the buffer register will be the erroneous bit.

- Therefore, the only syndrome that needs to be detected is . This can be accomplished with a single three-input AND gate. Which gives the output only if the contents of the syndrome register are , otherwise .

- We now refer to this specific single three-input AND gate circuit as the Error Pattern Detector (EPD) in our current experiment. The complete decoding circuit is shown in Figure 6.

The decoding procedure of the Meggitt decoder for cyclic code generated by (see Figure 6) is summarized below.

The contents of all shift registers are initialized to zero.

Turn on Gate 1 and Gate 2.

Turn off Gate 1 after time instances, i.e., when the computations in the syndrome circuit corresponding to all received bits are completed.

So, after time instances, the contents of the buffer register will form the received vector and its syndrome in the syndrome register. Hereafter, the remaining task is the detection and correction of an erroneous bit in the received vector. To remove the error effect in the received vector and syndrome, the properties of that are discussed earlier are utilized (properties 2(a) and 2(b)). This procedure is executed as follows:

- The contents of the shift register (syndrome) are fed to the EPD. If the syndrome , the output of the EPD is . It indicates that the bit is erroneous. So, the output of the detector is fed to the syndrome circuit and buffer register along with the shifting operation. Therefore, contents in the buffer register is and the syndrome is formed in the syndrome register. Clearly, we can see that from the property 2(a) the syndrome of the vector is . Through this operation, the error effect is nullified in both the received vector and syndrome vector. The output of the buffer register is .

- Suppose the syndrome , the output of the EPD is . It indicates that the bit is not erroneous. The output of the detector is fed to the syndrome circuit and buffer register along with the shifting operation. Therefore, contents in the buffer register is and the syndrome is formed in the syndrome register. From property 2(b), the syndrome formed in syndrome register is syndrome of . The output of the buffer register is .

This process will continue up to time instants, serially bit by bit, until the entire received vector is read out of the buffer register.

Suppose the error location is , then the content in the syndrome register will be at shift, and after that in every shift the syndrome will be zero.

The decoded vector will be formed at the 7th shift cycle in the buffer register.

Now we will explain the decoding process through an example.

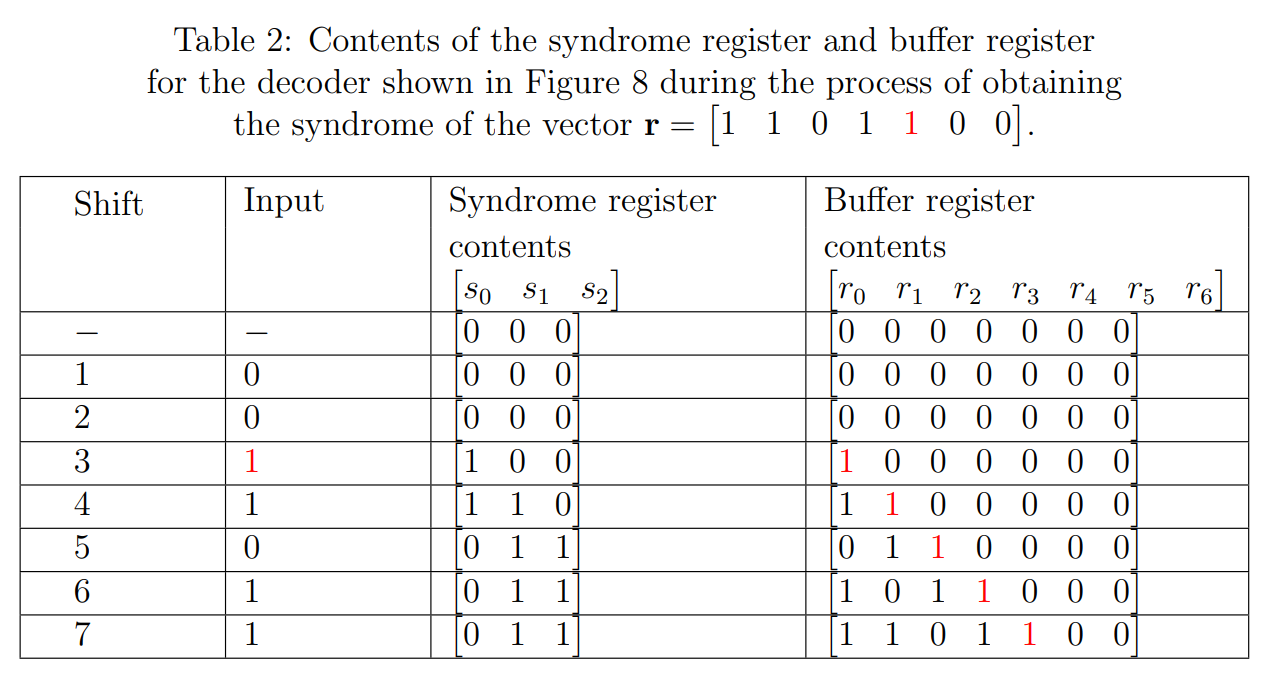

Suppose that the codeword is transmitted and is received. Then, the received polynomial and single error occurred at .

At first, the syndrome will be formed after entering the entire received vector by turning on Gate 1 and Gate 2 in the decoder (Figure 6). At the initial state, both the syndrome register and the buffer register contain all zeros. Notice that at each time instant, the operation takes place in the syndrome register is , and in the buffer register, the received bits are entered bit by bit. During the process of determining the syndrome of the received vector , the contents of both the syndrome register and the buffer register at each time instant are given in Table 2.

Therefore, the syndrome of the received vector is . The detection and correction task is performed by disabling Gate 1 and enabling Gate 3. Decoding will be done bit by bit, from the highest-order received bit to the lowest-order received bit . We denote the shift cycle with . After decoding the received bit , both the buffer and syndrome register are shifted once to the right. The next received bit to be decoded is . At each shift cycle, the contents of the syndrome register and the received vector in the buffer register are updated with the output of the EPD. Notice that at each shift cycle, the operation takes place in the syndrome register is

The output of the decoder at th shift cycle is , and it is the decoded bit of the received vector bit . The error correction process of the circuit shown in Figure 6 is given in Table 3.