Delay Estimation In Chain Of Inverters

In this experiment, the goal is to calculate the propagation delay when a load is driven by a chain of inverters. We begin with a simple case: a single inverter driving a capacitive load .

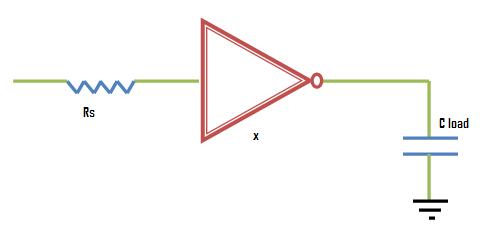

Sizing a Single Inverter

When optimizing the size of an inverter (), driven by a source resistance and driving a load :

- Large inverter size: Drives quickly, but struggles due to increased input capacitance.

- Small inverter size: drives quickly, but delay to increases.

There is an optimal point between these extremes.

Effect of Scaling:

- If inverter size is scaled by :

- Resistance decreases by

- Capacitance increases by

Optimal Condition:

An inverter is scaled for optimum delay when the RC product of its input capacitance and the external resistance driving it equals the RC product of its output resistance and the external load that it drives.

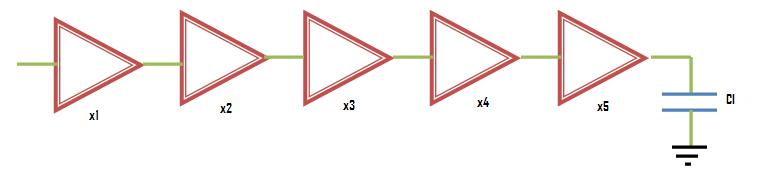

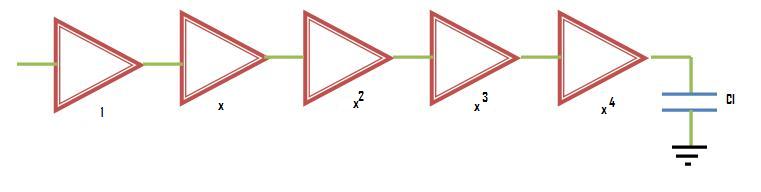

Chain of Inverters

Extending the concept to a chain of inverters:

To minimize delay, the RC product at input and output of each inverter should be the same. The optimum size of each inverter is the geometric mean of its neighbors. If each inverter is sized up by the same factor with respect to the preceding inverter, it will have the same effective RC product and hence the same delay.

Example: Chain of Five Inverters

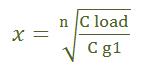

Optimum Sizing Factor

The value of (scaling factor) is:

Where:

- = number of inverters in the chain

- = load capacitance

- = input gate capacitance of the first inverter

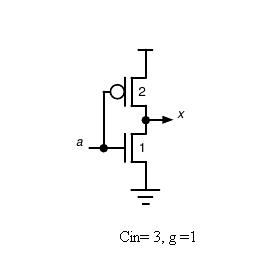

Delay in Logic Circuits and Logical Effort

One of the common challenges in chip design is determining the optimal transistor size and number of logic stages to minimize delay. The method of logical effort is used to estimate delay in CMOS circuits, accounting for capacitive load and gate topology.

Gate delay formula:

Where:

- = intrinsic delay

- = effort delay

Effort delay:

Where:

- = logical effort (ratio of gate input capacitance to inverter capacitance when sized for equal current)

- = electrical effort (), a function of load/gate size

Logical effort of an inverter is 1:

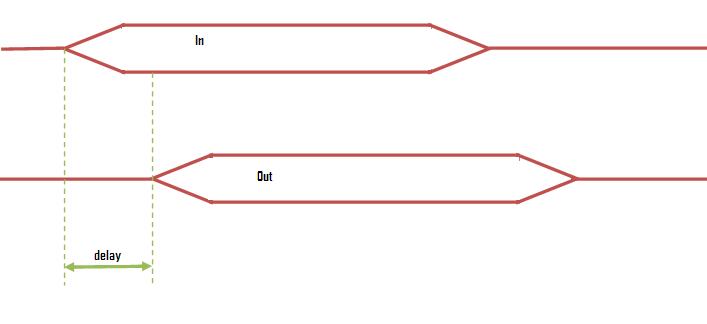

Delay Illustration

In this experiment, you will learn how delay can be reduced by changing the gate size of an inverter.

The goal is to reduce the time between input and output transitions by optimizing gate sizing in a chain of inverters.

Summary Table: Delay Parameters

| Parameter | Description |

|---|---|

| Source resistance | |

| Load capacitance | |

| Input gate capacitance of first inverter | |

| Sizing factor for each inverter | |

| Number of inverters in the chain | |

| Logical effort | |

| Electrical effort | |

| Intrinsic delay | |

| Effort delay | |

| Total delay |