Performance measurement and analysis of DC-DC buck regulator

Theory

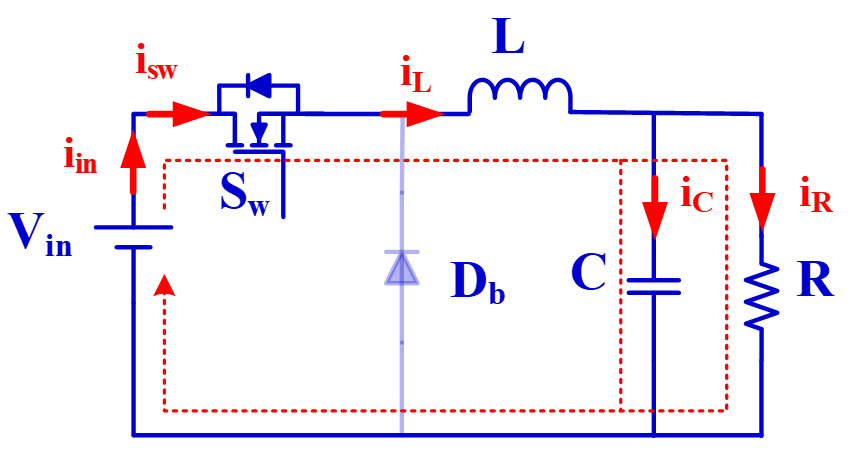

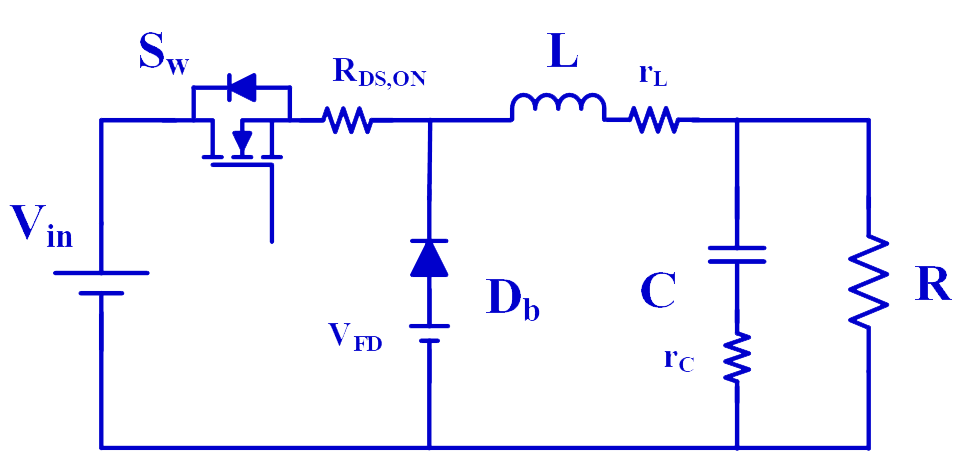

The circuit configuration of buck converter is given in Fig. 1.

Fig.1 Circuit configuration of Buck Converter.

Based on the operation of switch (Sw: ON/OFF-state) the operating principle of the converter is explained below briefly.

|

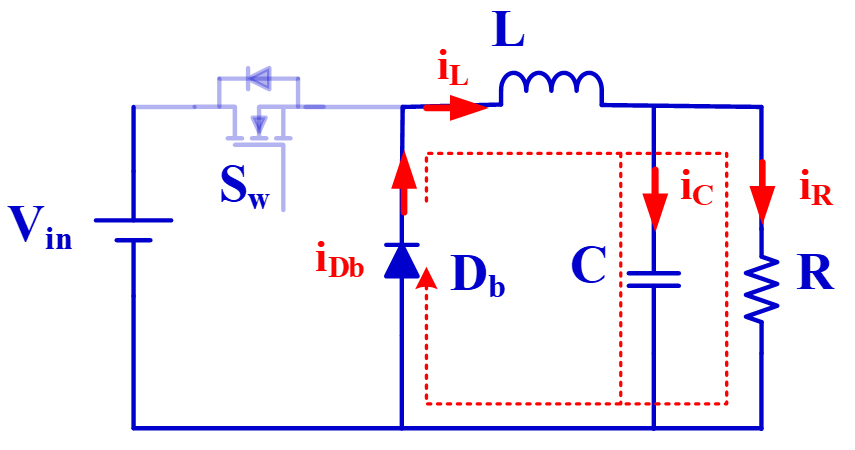

Mode – I : Switch (Sw): ON and Diode (Db): OFF

|

Mode – II : Switch (Sw): OFF and Diode (Db): ON

|

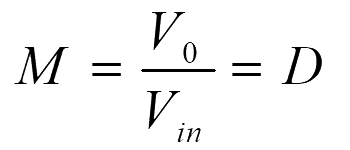

a) Voltage conversion ratio or voltage gain (M)

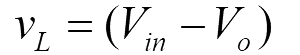

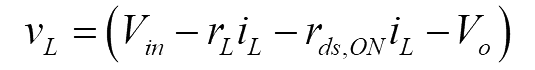

Voltage across inductor L:

Mode – I :

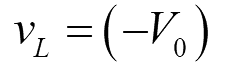

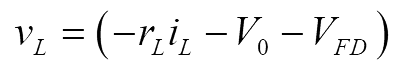

Mode – II :

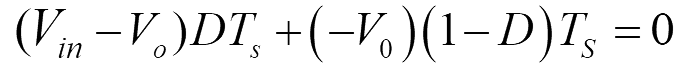

Applying volt-sec balance on inductor (eqn. 1 and 2)

On solving eqn. 3

b) Average current through inductor (IL):

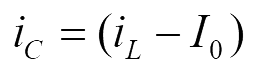

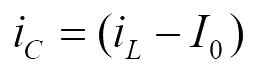

Current through capacitor

Mode – I :

Mode – II :

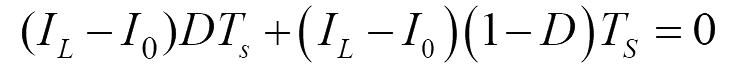

Applying charge-sec balance on capacitor (eqn. 5 and 6)

On solving

Therefore, average inductor current is load current.

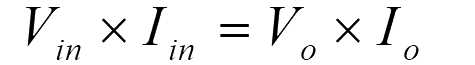

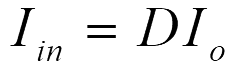

c) Power balance under ideal condition (neglecting losses):

Under ideal condition, input power must be equal to output power, hence

Substituting eqns. 4 and 10

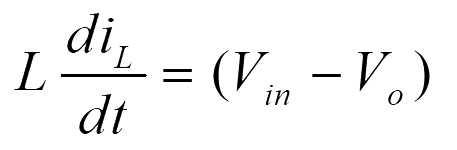

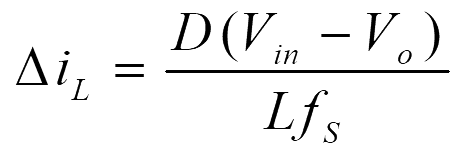

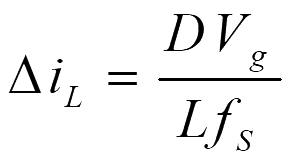

d) Inductor current ripple:

From eqn. 1,

Therefore, the inductor ripple current is

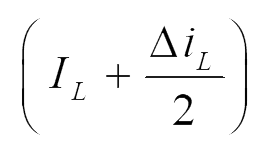

e) Current through various components:

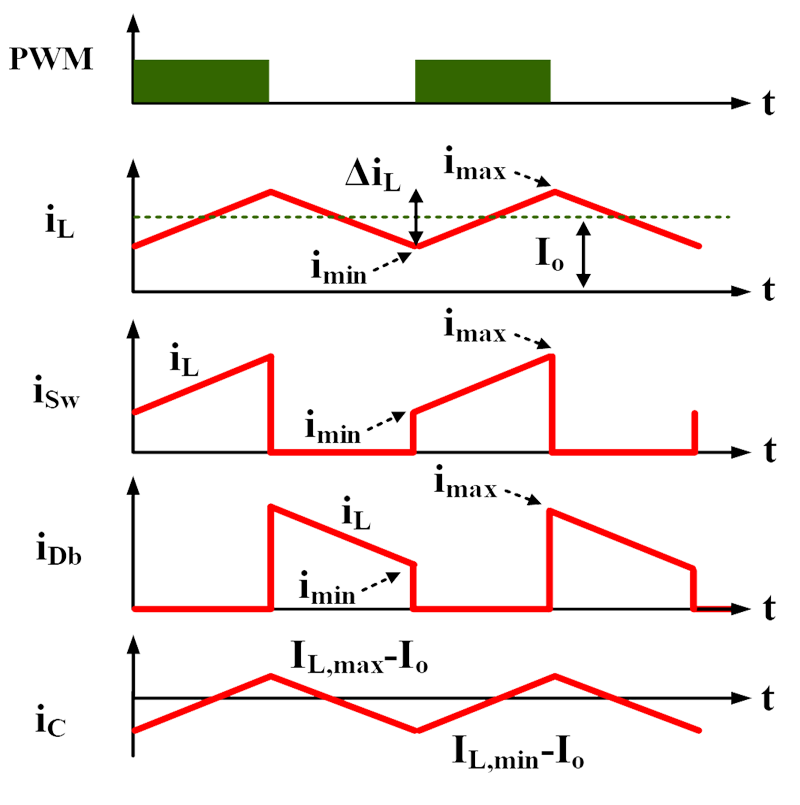

The current through various components is given in Fig. 3.

Fig. 3 Current through various components.

|

Mode-I (DT) |

Mode-II (1-D)T |

Average Current | |||

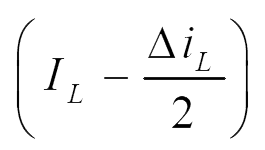

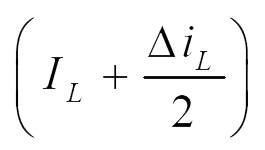

| imin | imax | imin | imax | Iavg | |

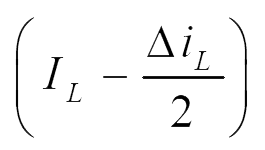

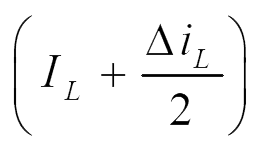

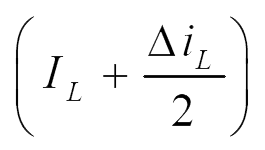

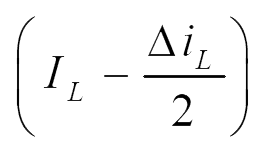

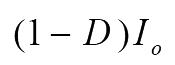

| iL |  |

|

|

|

|

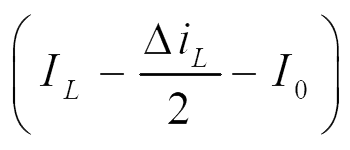

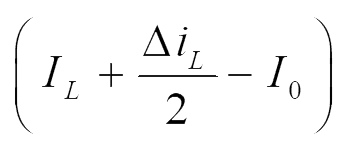

| iC |  |

|

|

|

0 |

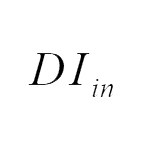

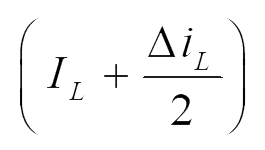

| iSw |  |

|

0 | 0 |  |

| iDb | 0 | 0 |  |

|

|

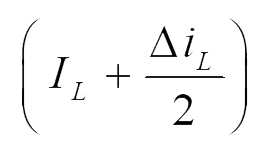

f) Voltage and current stress on various components:

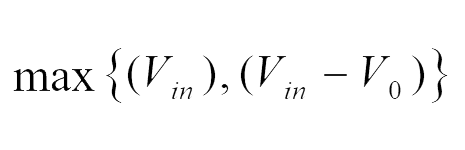

| Component | Voltage stress | Current Stress |

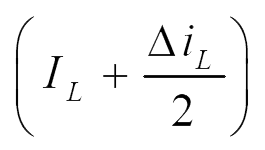

| Inductor (L) |  |

|

| Capacitor (C) | V0 |  |

| Switch (Sw) | Vin |  |

| Diode (Db) | Vin |  |

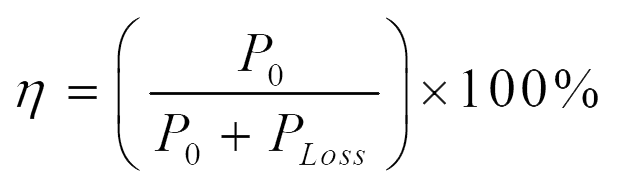

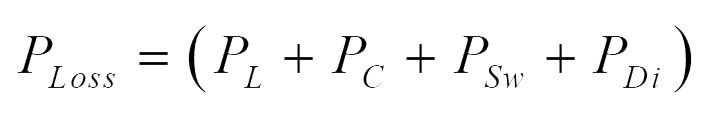

g) Efficiency analysis:

The power loss occurring in various components are given below.

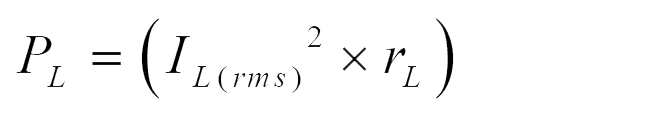

Power loss in inductor:

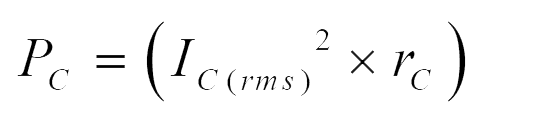

Power loss in capacitor:

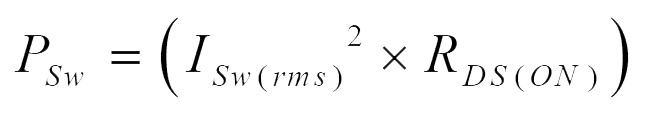

Power loss in switch:

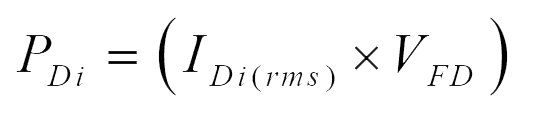

Power loss in Diode:

Total power loss:

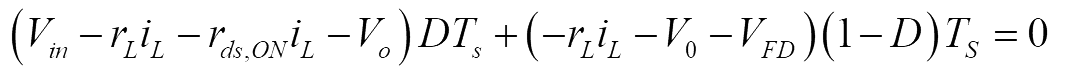

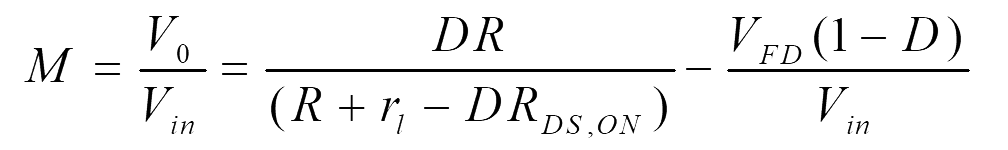

h) Effect of non-idealities on voltage gain expression:

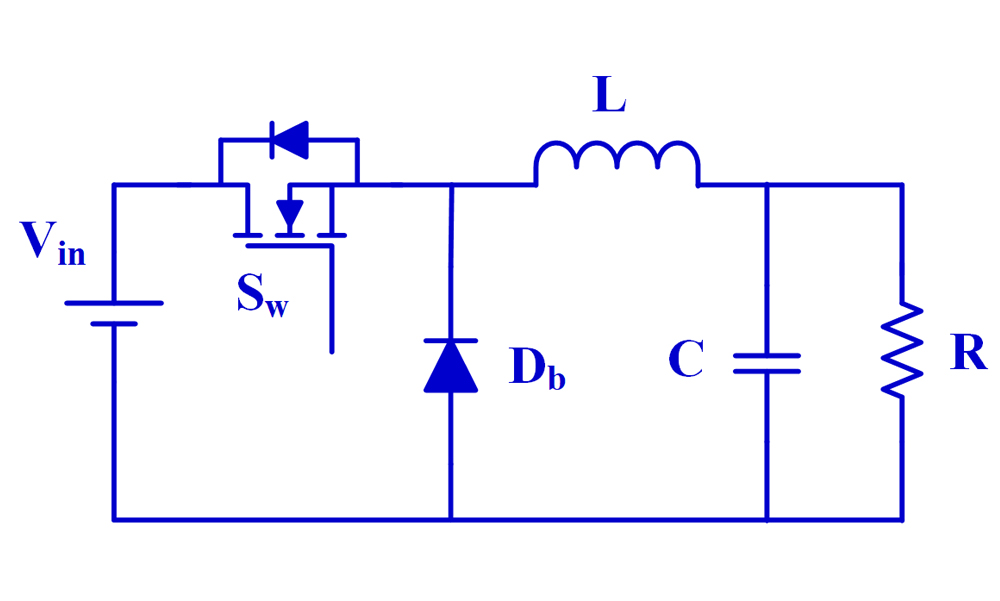

Fig. 4 Circuit configuration of conventional buck converter with non-idealities

Voltage across inductor L

Mode – I :

Mode – II :

Applying volt-sec balance on inductor (eqn. 22 and 23)

Simplifying eqn. (24) results in

(Effect of rc is not considered for simplification of equation)