Design of Adder circuit using Verilog

This page provides a comprehensive overview of adder circuits and their implementation in Verilog. We will explore two fundamental adder designs:

- Half Adder

- Full Adder

Understanding Adder Circuits

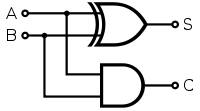

Half Adder

A half adder is the most basic form of adder circuit that adds two single-bit binary numbers. It has two inputs ( and ) and two outputs ( and ).

Circuit Diagram

Boolean Expressions

- Sum (): (XOR operation)

- Carry (): (AND operation)

Truth Table

Verilog Implementation

module half_adder(

input A,

input B,

output Sum,

output Carry

);

// Sum is XOR of A and B

assign Sum = A ^ B;

// Carry is AND of A and B

assign Carry = A & B;

endmodule

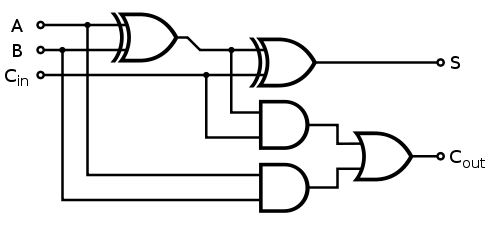

Full Adder

A full adder is an enhanced version of the half adder that can add three single-bit binary numbers. It has three inputs (, , and ) and two outputs ( and ).

Circuit Diagram

Boolean Expressions

- Sum ():

- Carry ():

Truth Table

Verilog Implementation

module full_adder(

input A,

input B,

input Cin,

output Sum,

output Cout

);

// Intermediate signals

wire sum1; // Output of first XOR

wire carry1; // Output of first AND

wire carry2; // Output of second AND

// First half adder

assign sum1 = A ^ B;

assign carry1 = A & B;

// Second half adder

assign Sum = sum1 ^ Cin;

assign carry2 = sum1 & Cin;

// Final carry

assign Cout = carry1 | carry2;

endmodule

Key Concepts in Verilog Implementation

1. Module Structure

- Module Declaration: Defines the interface of the circuit

- Port Declaration: Specifies inputs and outputs

- Internal Signals: Declares wires for intermediate connections

- Assign Statements: Implements combinational logic

2. Data Types

- input: For input ports

- output: For output ports

- wire: For internal connections

- reg: For testbench signals

3. Operators

- : Bitwise XOR

- : Bitwise AND

- : Bitwise OR

- : Bitwise NOT

4. Design Considerations

Combinational Logic

- Use

assignstatements for combinational circuits - Avoid feedback loops

- Consider propagation delays

- Use

Signal Declaration

- Declare all signals before use

- Use meaningful names

- Follow naming conventions

Port Connections

- Match port directions (input/output)

- Maintain consistent bit widths

- Use named port connections in testbench

Applications of Adder Circuits

Arithmetic Logic Units (ALU)

- Basic building block for arithmetic operations

- Used in processors and microcontrollers

Digital Signal Processing

- Part of digital filters

- Used in signal processing algorithms

Cryptography

- Used in encryption algorithms

- Part of hash functions

Error Detection

- Used in parity checkers

- Part of error correction codes

Performance Considerations

Propagation Delay

- Half Adder: gate delays

- Full Adder: gate delays

Power Consumption

- Depends on switching activity

- Affected by input patterns

Area Requirements

- Half Adder: gates

- Full Adder: gates

Testing and Verification

Functional Testing

- Verify all input combinations

- Check output waveforms

- Validate timing requirements

Testbench Structure

- Input signal generation

- Output monitoring

- Error checking

Simulation

- Use waveform viewer

- Check timing diagrams

- Verify functionality

Note: This theory guide focuses on the fundamental concepts of adder circuits and their Verilog implementation. For practical implementation steps, refer to the procedure.md file.